摘要

三相LCL型逆变器具有高频抑制明显和体积较小的优点, 但LCL型滤波器固有谐振峰易导致系统不稳定. 本文设计了基于分数阶线性扩张状态观测器(FOLESO)的分数阶自抗扰控制(FOLADRC)策略, 利用FOLESO的扰动补偿特性有效地抑制了系统的谐振峰. 在此基础上, 引入了具有无相移低通滤波器和降阶型频率自适应相位滞后环节的改进重复控制(RC)策略, 进一步提高系统对周期性电流谐波抑制能力. 本文还给出了改进重复控制–分数阶自抗扰控制(RCFOLADRC)策略的详细设计过程、参数选择方法和相关性能分析. 仿真和实验结果表明, 所提出RC-FOLADRC在保证电流跟踪性能的基础上, 对电网阻抗变化、LCL滤波器参数变化和电网频率波动有很强的鲁棒性, 能够有效地应用于LCL型逆变器并获得较为理想的并网电流.

Abstract

A three-phase LCL inverter has the advantages of significant high-frequency suppression and compact size. However, the inherent resonance of the LCL filter can easily lead to system instability. In this paper, a fractional order linear active disturbance rejection control (FOLADRC) based on fractional order linear expansion state observer (FOLESO) is designed. The disturbance compensation characteristics of FOLESO are used to suppress system resonance. On this basis, an improved repetitive control (RC) with a phase-shift-free low-pass filter and a reduced-order frequency-adaptive phase lag link is introduced to further enhance the system’s capability to suppress periodic current harmonics. The detailed design process, parameter tuning, and related performance analysis of the improved repeated control-fractional order linear active disturbance rejection control (RC-FOLADRC) strategy are provided. Simulation and experimental results demonstrate that the proposed RC-FOLADRC exhibits strong robustness to disturbances in grid impedance, LCL filter parameters, and grid frequency, while ensuring accurate current tracking performance. Therefore, the RC-FOLADRC can be effectively applied to LCL inverters, resulting in optimal grid-connected current.

1 Introduction

Nowadays, it has become an inevitable trend to develop new energy power generation for sustainable economic development [1] . As the crucial intermediate link of new energy power generation into the power grid, the three-phase LCL inverter has the advantages of highfrequency harmonic suppression and a compact size, which is extensively used in distributed power generation systems [2] . However, the inherent high-frequency resonant peak of LCL filter can easily lead to systeminstability. At the same time, the mathematical model of LCL filter in dq coordinate system is complex, and there is serious parameter coupling, which requires high robustness of the controller. Non-ideal factors such as space vector pulse width modulation (SVPWM) and dead-time effect, also cause periodic harmonics in the grid-connected current of LCL inverter. These current harmonics can cause grid pollution and affect the safe operation of electrical equipment [3] . The traditional PI control has no suppression effect on the resonance of LCL filter. It needs to sacrifice bandwidth to suppress the resonance peak or adding additional resonance suppression methods. The commonly used methods for suppressing resonance are passive and active damping methods. Passive damping suppresses the resonant peaks by applying resistors in series or parallel to L or C of the LCL filter. This method is simple and effective. However, it will reduce the filtering effect and increase the energy loss [4] . Active damping adopts a control algorithm to simulate passive damping to suppress internal resonance and avoid energy loss, but it needs to add additional sensors [5], which will lead to an increase in hardware cost. Therefore, many scholars use state observer to estimate unknown state variables through the known state variables, so as to suppress resonant peaks. In [6-7], the active disturbance rejection control (ADRC) , proposed by Han Jingqing and Gao Zhiqiang et al, estimates the sum of all internal and external disturbances using the extended state observer and implements compensation in a feedforward manner. ADRC can effectively compensate for external environmental disturbances and internal disturbances such as system parameters variation and inherent resonance. This method has been gradually applied to the current control of LCL grid-connected inverters and has achieved certain research results [8] . In [9], a fourth-order ADRC is designed for the current loop of three-phase LCL gridconnected inverter. The fourth-order ADRC can effectively decouple and suppress inherent resonance while saving sensors. However, there are many parameters to be tuned and the relationship among them is complex, which makes the tuning process difficult. In [10], the Pade trick is used to approximate the third-order controlled object in order to design the second-order ADRC. Although the controller parameters are reduced, the anti-disturbance capacity of the system is limited by the observation capability of traditional linear extended state observer (TLESO) , which can easily destabilize the system. In [11], an active filter is embedded in thetraditional linear ADRC (TLADRC) , which could suppress resonance, achieve internal decoupling and filter specific harmonics. However, the accuracy of harmonic current detection has a great impact on the result of harmonic filtering. The robustness of this method is not strong, and the bandwidth of its current loop is limited by TLESO.

Grid current harmonic suppression is another essential problem for three-phase LCL inverter. Numerous scholars have proposed many current harmonic suppression strategies, such as model predictive control, proportional resonant control, dead-time compensation, repetitive control, and so on. Model predictive control has the advantages of fast dynamic response and simple design of complex control systems, which can effectively reduce the harmonic content. However, the control performance is easily affected by parameter disturbances of LCL inverter [12-13] . In [14], the method of dead-time compensation is applied to compensate the current harmonics caused by dead-time, which can greatly improve the sinusoidality of current. However, this method is easily affected by the sampling accuracy of current and voltage, and it cannot suppress the current harmonics caused by factors other than dead-time. Proportional resonant control can effectively filter out specific frequency harmonics. However, it is unable to handle periodic harmonic disturbances that have integer multiples of the grid frequency [15-16] . Repetitive control (RC) can effectively suppress the periodic disturbances introduces by SVPWM. However, it has inherent phase lag, poor frequency adaptability, and requires a large amount of calculation [17-18] .

Considering the characteristics of TLADRC and RC, this paper introduces a fractional calculus term into TLADRC to improve the observation capability of TLESO, which could suppress LCL resonant peak and enhance the robustness of the system. An improved RC is used to further suppress the periodic current harmonics. Aiming at the notch offset problem of the traditional RC low-pass filter and phase-lag link, a phaseshift-free low-pass filter and a reduced-order frequencyadaptive phase-lag link are used to effectively improve the frequency adaptability and notch accuracy of the controller. In this way, the computational resources are saved and the result of periodic current harmonic suppression is improved. The parameter tuning method is provided, and its superior performance is demonstrated through simulation and experiment.

(1)

The rest of this article is organized as follow. Section 2 introduces the three-phase LCL grid-connected inverter. In section 3, fractional-order linear ADRC (FOLADRC) control strategy is presented. Parameter tuning and performance analysis are included. RCFOLADRC control strategy is presented in section 4 while parameter tuning is included. Performance analysis of RC-FOLADRC are introduced in section 5. Insection 6, experiment results are illustrated and analyzed. Section 7 concludes this article.

2 Three-phase LCL grid-connected inverter

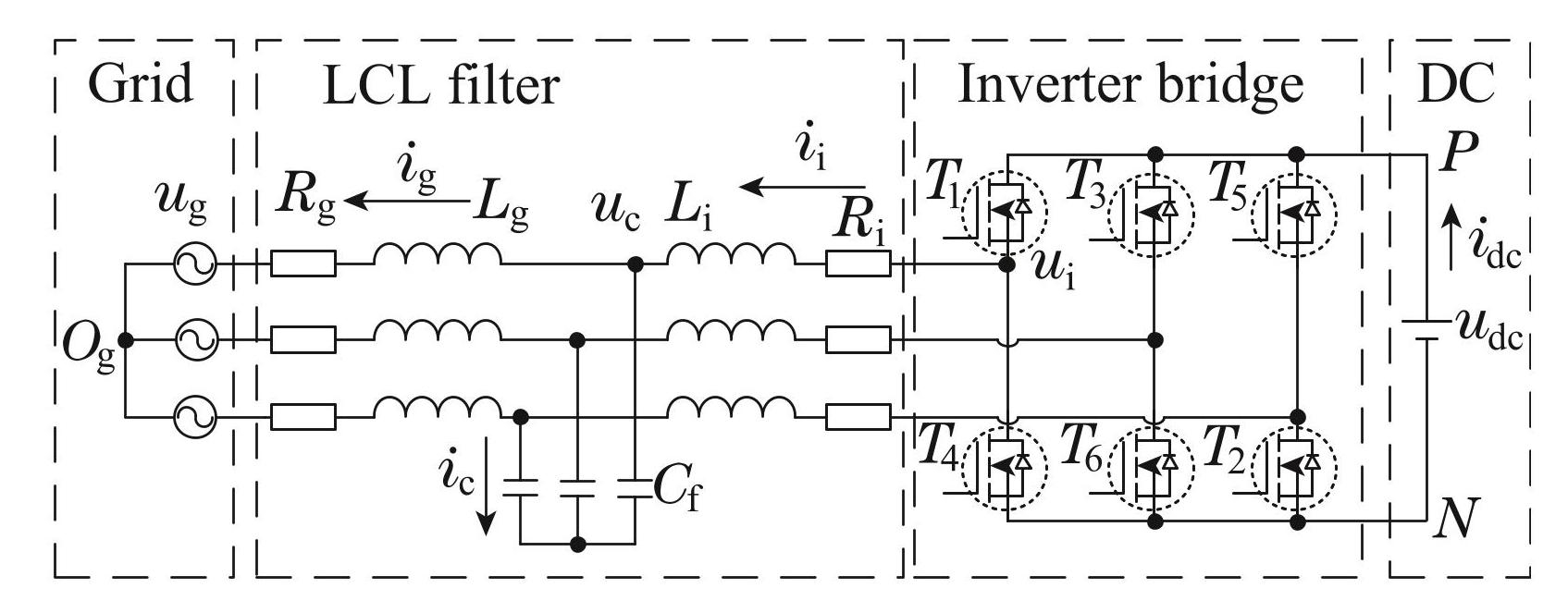

Fig.1 shows the circuit topology of the three-phase LCL pulse-width modulation (PWM) grid-connected inverter. The arrow in Fig.1 indicates the positive direction of current. ug is the grid phase voltage. ui is the inverter side phase voltage. ig and ii are the gridconnected side phase current and inverter side current, respectively. uc and ic are the voltage and current of the filter capacitors, respectively. Lg and Rg are the gridconnected side inductor and parasitic resistance, respectively. Li and Ri are the inverter-side inductor and parasitic resistance, respectively. Cf is the filter capacitor. udc is the bus voltage. The parameters of the LCL filter are Li = Lg = 1.0 mH, Rg = Ri = 0.1Ω, and Cf = 20 µF.

Fig.1Topology of three-phase LCL PWM grid-connected inverter

The system has computation delay and modulation delay introduced by space vector PWM (SVPWM) . Let the transfer function be Gdelay (s) and use Pade trick to approximate [19]. The pure delay transfer function is as follows:

(2)

where TSVPWM is the lag time introduced by SVPWM, and usually TSVPWM = 1.5Ts, Ts is the sampling period. It will introduce an additional phase lag, resulting in a reduction of the phase margin and making the system more prone to becoming critically stable or even divergent. It needs to be considered when designing the algorithm.

Assuming that the circuit is a balanced three-phase system, the transfer function Gig/ii (s) from the inverterside current to the grid-side current without the coupling term, is given in (3) . Gp (s) is the transfer function from inverter side voltage to current which takes into account pure time delay caused by SVPWM, as shown in Eq. (1) .

(3)

3 FOLADRC control strategy

3.1 Design of TLADRC

Since the d-axis current id and q-axis current iq are symmetric in the dq coordinate system, the grid-sidecurrent control is easily affected by the inherent resonant peak of LCL which leads to system divergence. Therefore, this paper introduces the control strategy of the d-axis inverter side current iid. According to Fig.1, the current on the side of d-axis inverter satisfies the differential equation

(4)

Let

where wg is grid frequency, iid, ucd are component on the d axis, iiq is component on the q axis. Construct the extended state space expression of LCL grid-connected inverter as follow:

(5)

where

b0 is the total gain of the shortest forward path. fd is the total d-axis disturbances. fd is bounded and differentiable which including known forward path disturbances, model information errors, and unknown disturbances such as errors introduced by the dead-time [20] .

Let z = [z1 z2] T, = z1, where z1 and z2 are used to estimate the controlled variable iid and the total disturbances fd, respectively. The state equation of TLESO is

(6)

where Az = A, Bz = B, Cz = C, L = [β1 β2] T, L is the error gain matrix of the linear extended state observer. Based on the estimated disturbance z2, the feedforward compensation is designed as follows:

(7)

where is to be determined afterward. When the observer converges, z2 is the estimate of total disturbances, in which case fd ≈ z2. By substituting Eq. (7) into Eq. (4) , we obtatin

(8)

The original plant is reduced to a1st-order integral system. The system can be effectively controlled as follow:

(9)

where rid is the given value of the d-axis inverter sidecurrent and k is the gain coefficient of controller.

3.2 Design of FOLADRC

The insufficient observation capacity of linear extended state observer (LESO) in TLADRC leads to insufficient decoupling, poor resonance suppression of the LCL filter, and low robustness. In this paper, the fractional calculus term is introduced to form fractionalorder LESO (FOLESO) to improve the disturbance observation capability which can effectively suppress LCL resonance, and improve the system’s robustness.

3.2.1 Principle

The control system structures of TLADRC and FOLADRC are shown in Fig.2 with yellow and black dashed boxes. Since the control law design method of FOLADRC is same as that of TLADRC, only the FOLESO design and implementation is introduced in this paper. To further improve the accuracy of disturbance observation, the state equation of FOLESO is set as follows:

(10)

whereis the Caputo fractional calculus operator with the order α and α ∈ [−1, 1]. P = [0 φ] T is the matrix which represents the error gain of the fractional calculus term. φ is a non-negative real number where φ = kββ2. It can be seen that the proposed FOLESO will regress into the form of TLESO when k = 0. According to Eqs. (5) – (6) (10) , the transfer function for estimation error of FOLESO can be obtained as follows:

(11)

where

Fig.2Control system structure of FOLADRC

The estimation error transfer function of FOLESO includes an adjustable term kββ2sα . This allows an increase in the adjustable degrees of freedom of the parameters, which is beneficial in expanding the width of the disturbance observation frequency band.

As shown in Fig.2, both TLESO and FOLESO are two-input single-output system with equivalent transferfunction as shown below:

(12)

where G12 (s) and G11 (s) of FOLESO have one more adjustable term kββ2s α than that of TLESO. G12 (s) and G11 (s) are expressed respectively as follows:

According to Eq. (12) and Fig.2, the open-loop transfer function Go (s) and the disturbance closed-loop transfer function Gd (s) of FOLADRC are as follows:

(13)

(14)

The fractional calculus term of FOLESO is implemented using the oustaloup trick for fitting sα [21], and it is discretized using the bilinear transformation method. Considering the amount of computation and the bandwidth of the control system, the fitting order is 4 and the fitting frequency band is [1e–5, 1e5] rad/s.

3.2.2 Parameter tuning

To guarantee the stability of the system. ωo satisfies ωo ∈ [3kp, 10kp] in engineering applications [22], so the control bandwidth kp = 2π × 330 and ωo = 1.288e4 rad/s are taken. After determining β1 and β2 using the bandwidth trick in [7], the bode diagram of the estimation error transfer function of FOLESO under different values of α and kβ are obtained from Eq. (11) as shown in Figs.3–4, respectively

Fig.3Bode diagram of estimation error transfer function for FOLESO with different α values

Fig.3 shows that when α <0, the accuracy of the estimation error for the low frequency improves with α decreases, which is inconsistent with the goal of suppressing the resonant peak of the middle-highfrequency. When α >0, increasing α improves the ac-curacy of estimation error in the middle-high-frequency, as well as enhances the capability to suppress disturbances. However, if α is too large, high resonance peak will be generated.

Fig.4 shows that FOLESO is equivalent to traditional TLESO when kβ = 0, where the estimation error is relatively high. As kβ increases, the estimation error gradually decreases. However, kβ that is too large will cause high-frequency resonance peak and lead to the increase in the estimation error at high-frequency. In summary, the parameters searching range of the fractional calculus term are set as α ∈ [0, 0.5], kβ ∈ [0, 0.1].

Using the phase margin Pm as the constraint condition, we obtain

(15)

where Pm = 30◦ ∼80◦ . The open-loop cutoff frequency ωc satisfies ωrp/10 <wc <ωrp/3. ωrp is the angular frequency of the positive resonant peak of LCL filter.

Fig.4Bode diagram of estimate error transfer function for FOLESO with different kβ values

The integral of time and absolute error (ITAE) is used to evaluate the dynamic performance of the system. The internet absolute error (IAE) is used to evaluate the disturbance rejection performance of the system.

(16)

rm = 15 is the rated current. Due to the small harmonic content at high frequency, kmax = 40 is desirable. Here, the main focus is on the disturbance caused by the dead-time and grid harmonics, specifically the harmonics of 6k frequency. Then Ak is the amplitude of the 6k harmonic of the inverter side current, ωk = 6k × 100π. Combined with Eqs. (8) – (9) , we can conclude that theequivalent closed-loop transfer function is a first-order inertial link. T0 and T1 are the integration time, and the value of T0 needs to be greater than the response time Tres of the closed-loop system.

(17)

Since the disturbance output signal iid (t) consists of the signal with the power grid frequency f0 and its integer multiple frequency, T1 = 5/f0 is desirable.

In order to consider both dynamic and disturbance rejection performance, the performance of system is evaluated using the following function:

(18)

where η1 = η2 = 0.5 is the weight coefficient, J can be find according to the range of Pm. In order to visually represent the impact of different parameters combination on the performance of system control, we define kβ, α and 1/J as the variables for the x-axis and y-axis and z-axis, respectively. The three dimensional surface diagram is plotted as shown in Fig.5. When α = 0.39 and kβ = 0.03, J gets the minimum value.

Fig.5Three-dimensional graphical relationship among the inverse of criterion function J, fractional order α, and gain coefficient kβ

3.2.3 Performance analysis

By substituting the specified parameters into Eqs. (13) – (14) , we can obtain bode diagrams of open-loop transfer function and the disturbance closed-loop transfer function for TLADRC and FOLADRC, as shown in Figs.6–7.

FOLESO increases the adjustable terms of the observer, so the flexibility of the observer and wo is increased. The observation ability of the system is enhanced, and the resonance peak of the system is effectively suppressed. Fig.6 shows that the open-loop cutoff frequency and phase margin of TLADRC and FOLADRC are similar and within a reasonable range. Therefore, they have similar dynamic characteristics.However, the positive resonance peak amplitude of FOLADRC is smaller which leads to the good performance in stability.

Fig.6Bode diagram of the open-loop transfer function for FOLADRC and TLADRC

Fig.7Bode diagram of the disturbance closed-loop transfer function for FOLADRC and TLADRC

Figure7 shows that, except for high frequency, FOLADRC has a higher attenuation gain for the disturbance, especially in the middle frequency. In the real system, the disturbance is mainly in the low-middle frequency. Therefore, FOLADRC has superior disturbance rejection performance in closed-loop system.

4 Improved RC-FOLADRC control strategy

The current harmonics of the grid-connected inverter are primarily concentrated at the frequency of integer multiples of the grid frequency. Considering the excellent suppression capability of the RC for periodic signals, the RC-FOLADRC strategy is further proposed by introducing an improved RC into the FOLADRC control structure. For the improved RC, a phase-shiftfree low-pass filter and a reduced-order adaptive link are used to improve the notch accuracy and frequency adaptability.

4.1 Design of improved RC

RC is easy to implement in digital controllers, and it is more effective to analyze its control performance in discrete systems. The sampling frequency of the system is 20 kHz, and the controlled plant and controller are discretized using zero-order hold (ZOH) trick and tustin trick, respectively. The discrete control system structure diagram of RC-FOLADRC is shown in Fig.8. In Fig.8, Q (z) is the phase-shift-free low-pass filter, S (z) is the compensation function, and d is the disturbance input. The discrete closed-loop transfer function of given value and the discrete closed-loop transfer function of disturbance are given by Eqs. (19) – (20) , respectively.

(19)

(20)

where

Grcp (z) is the transfer function of the inner loop, N = fs /f0, fs is the sampling frequency, f0 is the fundamental frequency of the disturbance signal.

4.1.1 Low pass filter Q (z)

The stability and disturbance rejection performance need to be considered when Q (z) is designed. Generally, the traditional first-order low-pass filter is used to achieve good stability. Although the order is low and the implementation is simple, it will introduce additional phase lag and shift the fundamental frequency of thenotch, which affects the frequency adaptability of the system. Since a phase-shift-free low-pass filter has zero phase shift, it is utilized in the design of Q (z) [23].

(21)

The sampling frequency fs is 20 kHz, and the cutoff frequency of the filter is ωc = 1.03e4 rad/s. Setting S (z) = 1, the bode diagram of with the traditional or designed Q (z) is shown in Fig.9.

The depths of the corresponding notches in the two methods are approximately equal. However, the fundamental frequency of the notch with the traditional first-order low-pass filter is 50.2 Hz, while it is 50 Hz with the phase-shift-free low-pass filter. Therefore, the designed method could improve notch accuracy which could better suppress 50 Hz and its integer multiple harmonics.

Fig.8Structural diagram of the equivalent discrete control system for RC-FOLADRC

Fig.9Bode diagram of with different Q (z) design methods

4.1.2 Phase lag link

The lag beat N of the traditional integer-order phase lag link z −N is a positive integer and fixed. The notch frequency accuracy is low, and it needs to occupy a lot of computational resources. Therefore, a reduced-order frequency-adaptive phase lag link is adopted, which is expressed as follows:

(22)

where fs is the sampling frequency, fPLL is the grid frequency estimated by phase-locked loop (PLL) , kN is the coefficient for adjusting the notch fundamental frequency, Np is the integer order, k (i) (i = 1, · · ·, n) is the coefficient of the fitting term, and n is the order of the fitting function. The harmonic disturbance frequency is concentrated at 6k (k = 1, 2, · · ·) times the grid frequency. If kN = 6, the maximum number of lag beats N is only 1/6 with kN = 1, which is conventionally set in the typical RC method. This can greatly reduce the amount of computing resources. Based on the expression of an ideal finite impulse response (FIR) [24] digital filter and the principle of minimum error, it can be obtained as follows:

(23)

where W is used to approximate fractional order time lag. Solving Eq. (23) , we have

(24)

(25)

where the symbol [·] denotes rounding. The closer W gets to n/2, the smaller the approximation error.

Considering the computation constraints and fitting accuracy, the order is chosen as n = 3. Since Q (z) introduces a lead link and its highest order nq = 3, the overall structure of the repetitive controller using a reduced-order frequency-adaptive phase-lag link is shown in Fig.10.

Fig.10Repetitive control structure diagram with reduced frequency-adaptive phase lag link

When the grid frequency is 51 Hz, lag beat N becomes 392.157. To compare the traditional and proposed methods, the Bode diagram for different design methods of the phase lag link is drawn, respectively, as shown in Fig.11.

When grid frequency becomes 51 Hz, the notch frequency of the traditional method still focus on 50 Hz and its integer multiple which leads to the result of harmonic suppression become worse. The notch frequency of the designed method can change with the grid frequency, while its notch depth can still be maintained.The designed method has a better adaptability to the variation of grid frequency. The harmonic suppression capability of the control system is improved. The effectiveness of the designed method can be verified.

Fig.11Bode diagram of with different design methods of phase lag link

4.1.3 Compensation function S (z)

Due to the influence of high frequency and the inherent resonance peaks, this paper adopts a compensation function design method based on the damping function. The compensation function is as follows:

(26)

The second-order low-pass filter is used to compensate for the amplitude and phase of the system at the low-middle frequency. The damped resonant angular frequency should not exceed the highest frequency of the desired harmonic suppression which is taken as 1600 rad/s. The damping ratio is ξ = 0.2. A firstorder low-pass filters are used to reduce the impact of unknown high frequency. Considering that a phase lag will be introduced, the cutoff frequency is usually higher than the damped resonant angular frequency mentioned above and lower than the positive resonant peak frequency, which is taken as 2000π rad/s. z m is a lead phase compensation link that is utilized to compensate for the phase lag introduced by the controlled plant and the compensation function. After the test, m = 14 has a good compensation effect and it is chosen in this paper.

5 RC-FOLADRC performance

5.1 Closed-loop stability

In order to verify the closed-loop stability of RCFOLADRC, an analysis is conducted on the pole-zero map of the closed-loop system. Based on Eq. (19) , Fig.12 illustrates the pole-zero map of the closed-loop transfer function. All poles are located inside the unit circle. It can be verified that RC-FOLADRC is stable in the discrete domain.

5.2 Step response

The step response process of the d-axis grid-connected side current of TLADRC and RC-FOLADRC from 10 A to 15 A is given in Fig.13. The figure shows that RC-FOLADRC is able to maintain similar dynamic response characteristics as TLADRC. The grid-side current can track its reference within 2 ms. Steady-state error of RC-FOLADRC is less than that of TLADRC.

Fig.12Pole-zero map of the closed-loop transfer function

Fig.13Step response waveforms of current on gridconnected side with different methods

5.3 Disturbance rejection performance

Based on Eqs. (14) – (20) , the Bode diagram of the disturbance closed-loop transfer functions of TLADRC and RC-FOLADRC is given in Fig.14. The figure shows that, compared with TLADRC, RC-FOLADRC has a superior disturbance rejection performance in close-loop system, especially at 6, 12 and 18 times the grid frequency. The suppression of 6k (k = 1, 2, · · ·) harmonic disturbances is stronger. RC-FOLADRC also has good low frequency rejection effect of disturbance. Compared with TLADRC, RC-FOLADRC has superior closed-loop disturbance rejection performance.

5.4 Robustness test

5.4.1 Grid impedance and grid-connected side inductance parameter variation

To test the performance of the proposed method with grid impendence or grid-connected inductance parameter variation, the inductance Lg is set as 0.9, 1 or 1.25 mH. The pole-zero map of Lg variation is given in Fig.15. The figure shows that all poles of the controlsystem are always located inside the unit circle when Lg varies. RC-FOLADRC is stable in the discrete domain when there are variations in the grid impedance and the inductance parameter of the grid-connected side.

Fig.14Bode diagram of the disturbance closed-loop transfer function

Fig.15Pole-zero map of the closed-loop transfer function with different Lg values

5.4.2 The filter capacitor parameter variation

To test the performance of the proposed method with filter capacitor parameter variation, the capacitor Cf is set as 18, 20, or 22 µF. The pole-zero map of Cf variation is shown in Fig.16. RC-FOLADRC is not sensitive to variation in Cf . The poles of the RCFOLADRC system are always located in the unit circle, indicating that it is stable.

In summary, the RC-FOLADRC can maintain stable operation of the system when there are variations in grid impedance and the parameters of the LCL filter.

6 Experimental Results

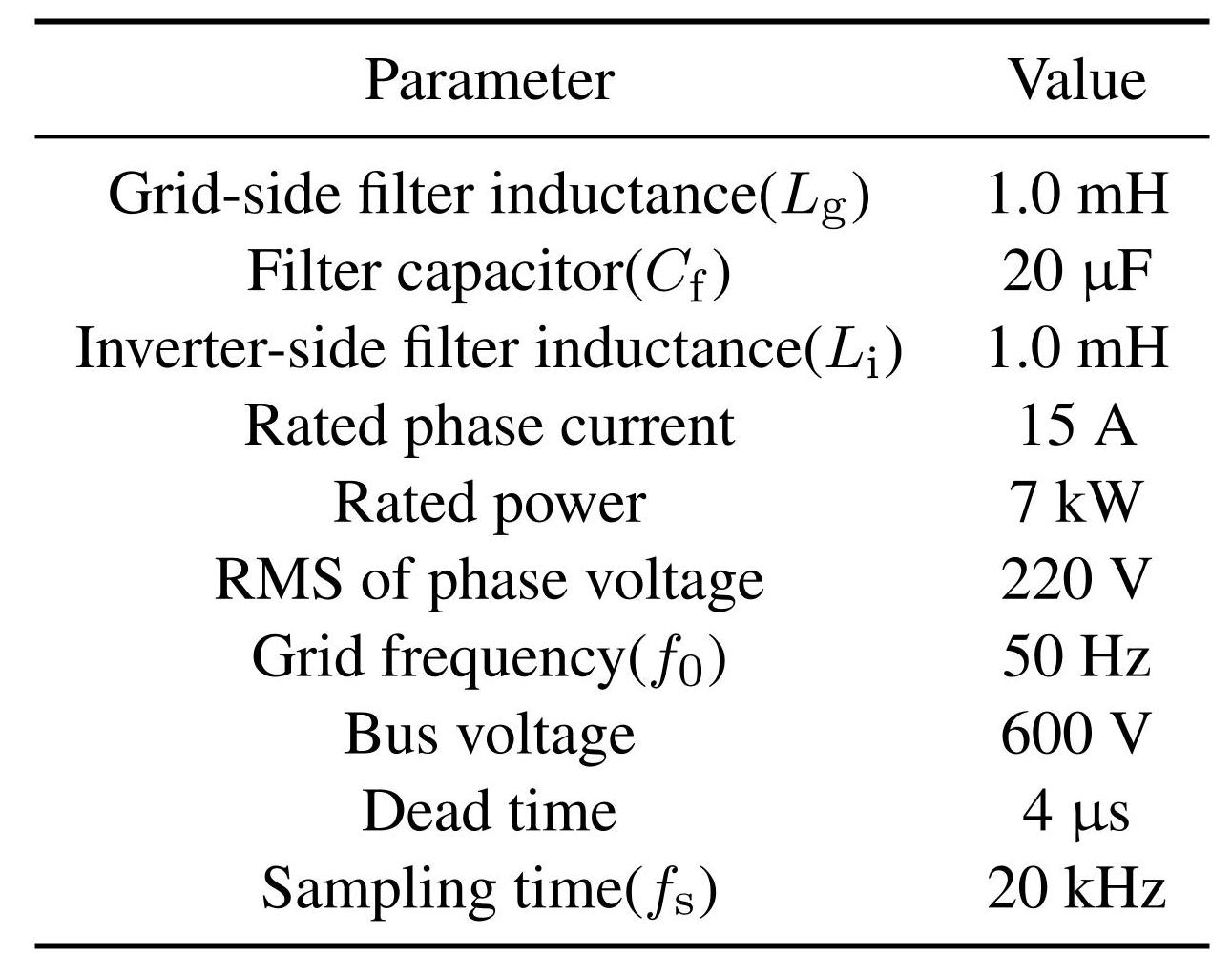

The experimental platform of the grid-connected inverter is shown in Fig.17. The parameters are shown in Table1. The clamp power meter is an electrical parameter analyzer that measures the power factor and total harmonic distortion (THD) . The digital oscilloscope can display voltage and current waveforms.

Fig.16Pole-zero map of the closed-loop transfer function with different Cf values

Fig.17Experimental platform of LCL inverter

Table1System parameters

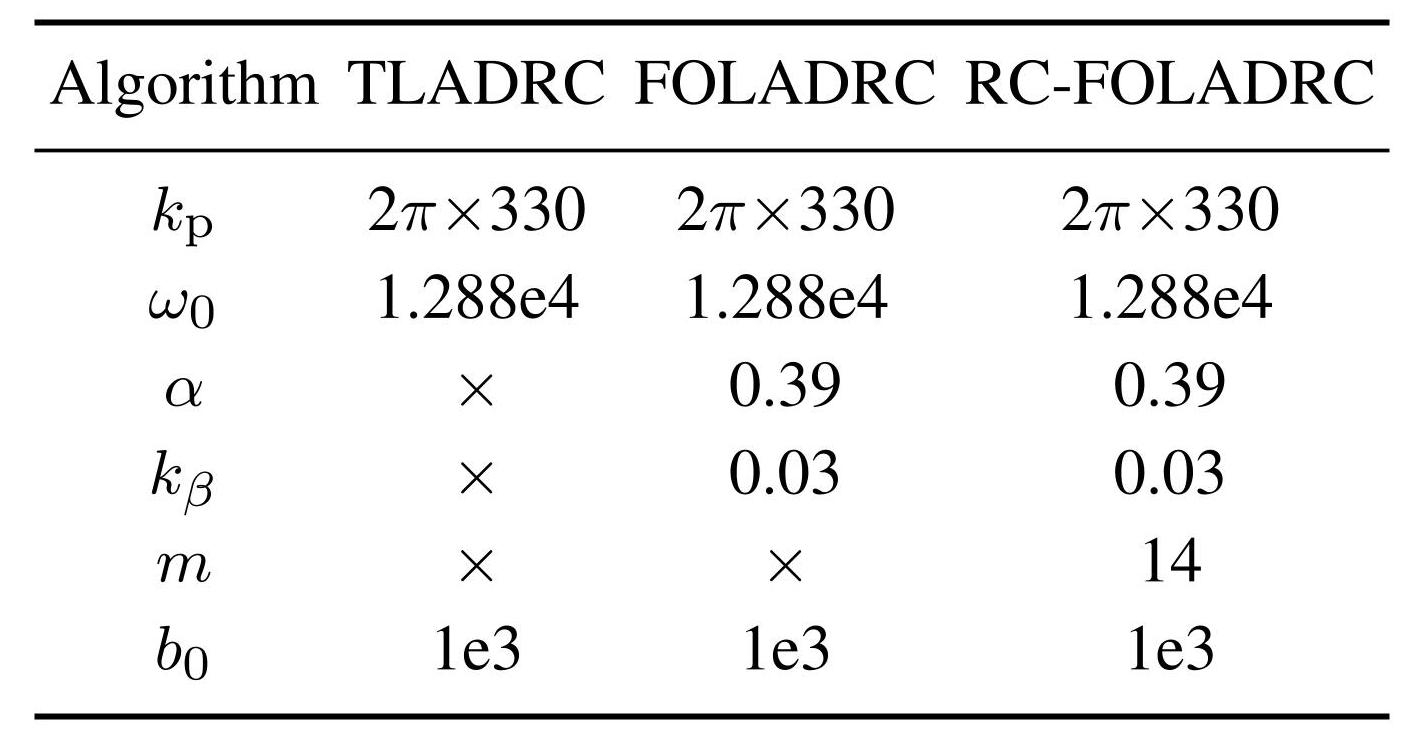

In this section, we will analyze and compare the control performance of RC-FOLADRC FOLADRC and TLADRC in practical applications. The control parameters are shown in Table2.

Table2Control parameters

6.1 Dynamic performance

The current on the d-axis of the inverter side get a step change from 10 A to 15 A. The waveforms of the phase voltage and phase current on the grid side of the TLADRC FOLADRC and RC-FOLADRC are obtained, as given in Fig.18.

Fig.18Transient response waveforms of grid-side current

The phase current can transition smoothly without any noticeable overshoot when the given value is changed. And RC-FOLADRC has smaller step fluctuations. The phase current can be stabilized after about 2.5 ms. Above controls exhibit good dynamic performance.

6.2 Steady-state performance

The steady-state performance experiment of the current loop is conducted by setting the d-axis current to 15 A. The waveform of phase voltage and phase current are shown in Fig.19, and the current harmonic component is shown in Fig.20.

Fig.19Steady-state waveforms of the grid-connected current

The current curve of RC-FOLADRC is smoother than that of FOLADRC. The power factor of three methods are close to 1, and the root mean square (RMS) current value is close to the target value of 10.61 A. They can achieve unity power factor control and high-precision current tracking. The THD of TLADRC is approximately 4.47%, whereas the THD of RC-FOLADRC is only 2.36%. The current harmonic suppression effect of RC-FOLADRC is highly significant. The total harmonic content of the current is lower, and it has better steady-state performance.

6.3 Robustness test

6.3.1 Grid impedance and grid-connected side inductance parameter variation

The variation in grid impedance is converted into inductance on the grid-connected side. The parameter variation experiments are carried out with the gridconnected side inductance Lg = 1.25 mH or 0.9 mH, respectively. The power quality analysis of the grid current is shown in Fig.21.

Fig.20Spectrum of steady-state current

According to Fig.21, when Lg is 0.9 mH and 1.25 mH, the THD of the grid-connected current of RCFOLADRC is 2.39% and 2.30%, respectively. It can meet the requirements of harmonic content in the grid current, and the difference is small compared to 2.36% when Lg = 1 mH. The fundamental RMS value has small change when grid connected inductance parameter and grid impedance variation. RC-FOLADRC has a good adaptability to variation of grid impedance and grid-connected side inductance parameter.

6.3.2 The filter capacitor parameter variation

The parameter variation experiments are carried out with the filter capacitor Cf = 18 µF or 22 µF, respectively. The power quality analysis of the grid current are carried as shown in Fig.22.

Fig.21Spectrum of steady-state current with different Lg values

It can be observed that the fundamental RMS value of the grid-connected current is close to the target RMS value of 10.61 when the filter capacitance Cf = 18 µF or 22 µF, respectively. This indicates that RC-FOLADRC has good current tracking accuracy, even though capacitor parameter variation exists. In addition, the THD of the grid current of RC-FOLADRCis 2.44% and 2.34%, respectively. The level of THD disturbance is relatively small. RC-FOLADRC has a good adaptability to variation of filter capacitor parameter.

Fig.22Spectrum of steady-state current with different Cf values

6.3.3 Grid frequency variation

In order to analyze the adaptability of the grid frequency of RC-FOLADRC, an experiment is conductedwith 49 Hz and 51 Hz the grid frequency, respectively, which lag beat N is 408.16 and 392.16. The diagram of the current harmonic components at different frequency is shown in Fig.23. The THD of 49 Hz and 51 Hz the grid frequency is 2.35% and 2.38% which have a very small change compared to the THD of 2.36% under 50 Hz the grid frequency. The fundamental RMS value has small change when grid frequency variation. RC-FOLADRC has good adaptability to variation of grid frequency.

Fig.23Spectrum of steady-state current with different grid frequency

In summary, the RC-FOLADRC is superior to the TLADRC in suppressing the harmonic component of the phase current. Meanwhile, it has good robustness to variation of grid impedance and LCL filter parameters. It exhibits good adaptability to disturbance of grid frequency. In the future, we will try to simplify the control algorithm while maintaining the same control effect.

7 Conclusion

In order to improve the inverter-side current control strategy of LCL inverter and enhance the system robustness, this paper proposes an improved RC-FOLADRC controller. Through theoretical analysis, simulation, and experimental validation, the following conclusions can be obtained.

1) Comparing with TLADRC, the proposed FOLADRC is more flexible by introducing fractional order calculus into the LESO item. And the estimate error can be further reduced.

2) The dynamic performance of the proposed FOLADRC is similar to that of TLADRC. FOLADRC has a more effective capability to reject disturbances and inherent resonance peak.

3) By combining the improved RC and the FOLADRC, the capability of periodic harmonic suppression is stronger. The improved RC algorithm adopts a reduced-order frequency-adaptive phase lag link which ensures the effectiveness of harmonic suppression against grid frequency variations.

4) The dynamic performance of RC-FOLADRC is similar to that of TLADRC. The capability of current harmonic suppression of the RC-FOLADRC algorithm is significantly better than that of TLADRC. The RCFOLADRC algorithm exhibits high capability in suppressing disturbances, such as LCL filter parameters, grid impedance and grid frequency.